- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

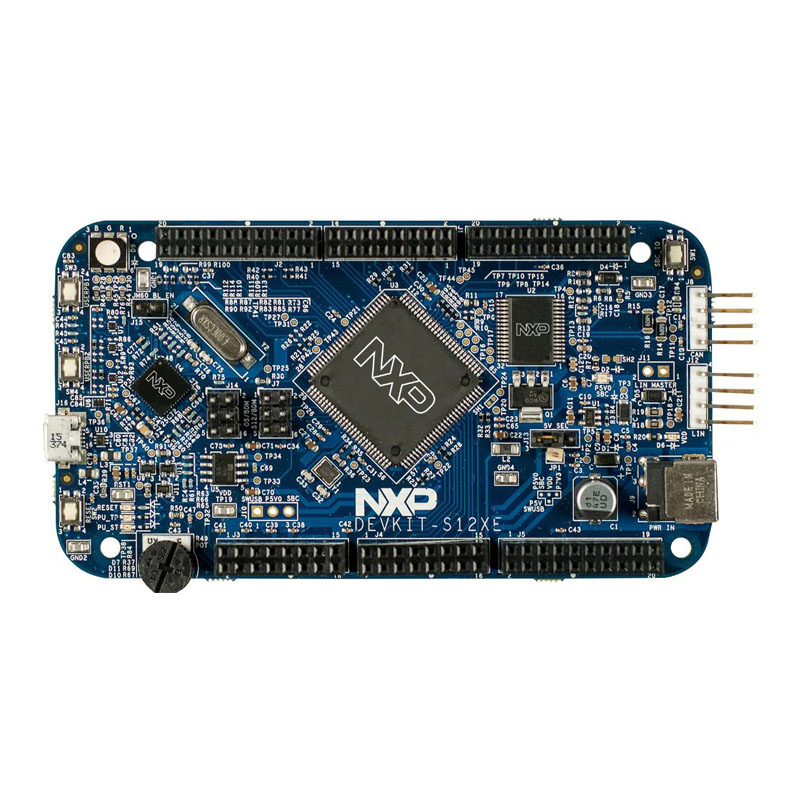

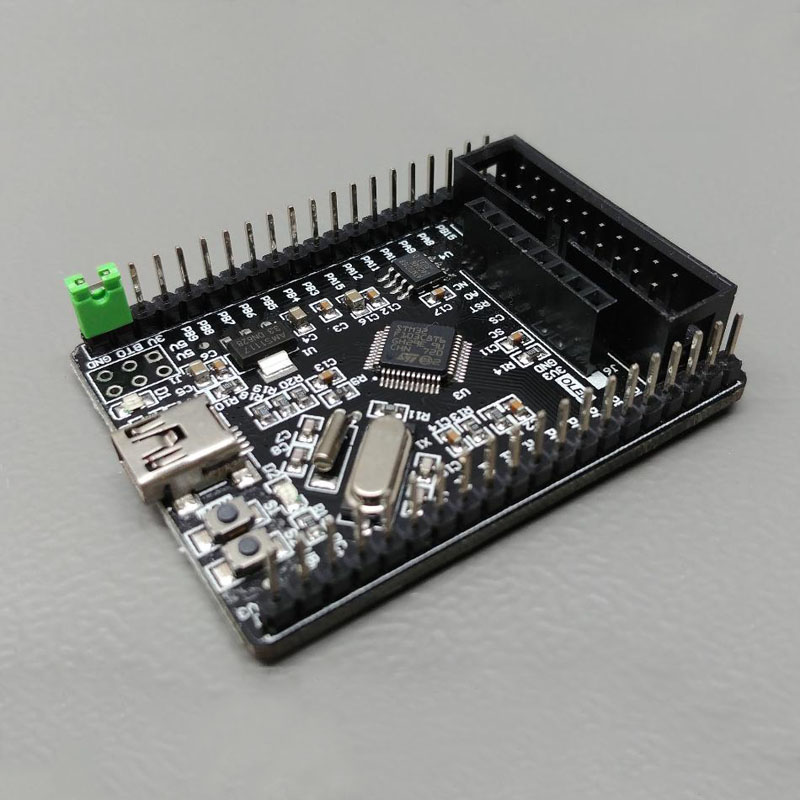

Scheda MCU ARM STM32

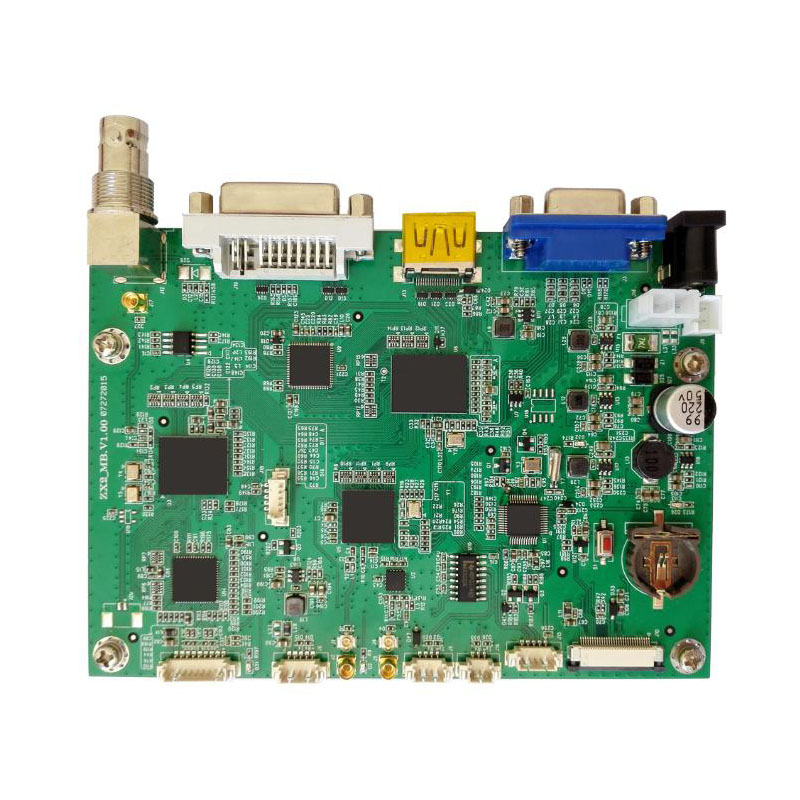

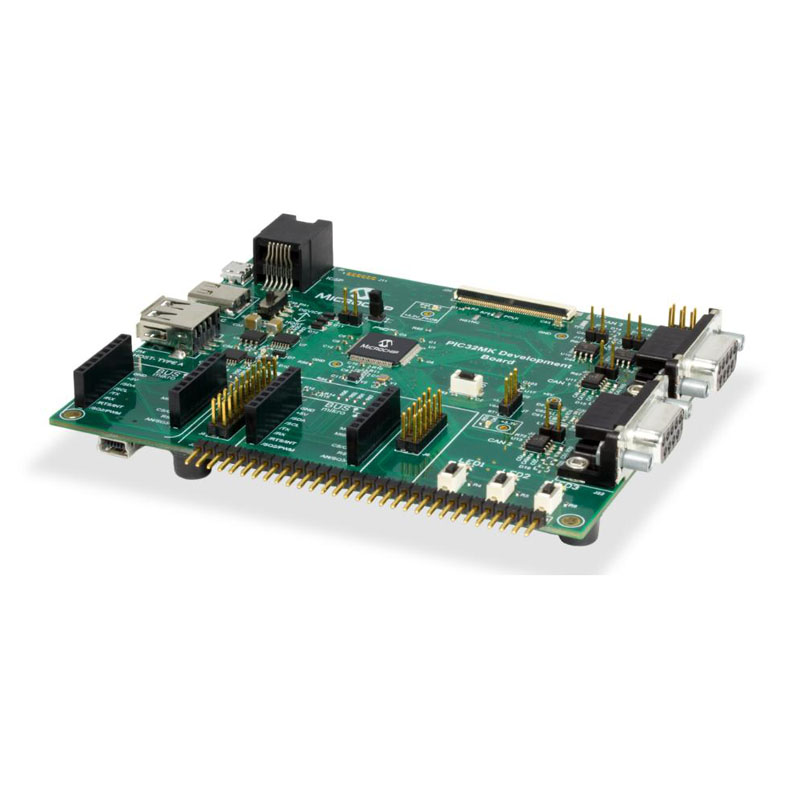

Ningbo Hi-tech Easy Choice Technology Co., Ltd è una società high-tech attiva nella progettazione, sviluppo e produzione della scheda MCU ARM STM32. La reputazione della nostra azienda si basa su un buon credito e sulla fornitura di un servizio eccezionale, che ha portato a collaborazioni a lungo termine con importanti società, agenzie governative e un'ampia comunità di utenti. Siamo specializzati nello sviluppo di schede di controllo elettronico intelligente, nella progettazione di prodotti di controllo meccanico ed elettrico, sviluppo di microcomputer a chip singolo, progettazione di circuiti e test di post-produzione. Possiamo progettare su misura il circuito di controllo per soddisfare le vostre esigenze, consentendo l'adempimento delle funzionalità previste del prodotto, sia che forniate requisiti funzionali espliciti o semplicemente un'idea.

Invia richiesta

YCTECH lo sviluppo della scheda di controllo del prodotto industriale comprende la progettazione del software della scheda di controllo industriale, l'aggiornamento del software, la progettazione di diagrammi schematici, la progettazione di PCB, la produzione di PCB e l'elaborazione di PCBA situati nella costa orientale della Cina. La nostra azienda progetta, sviluppa e produce schede MCU ARM STM32. Core: CPU ARM32-bit Cortex-M3, la massima frequenza operativa è 72MHz, 1.25DMIPS/MHz. Moltiplicazione a ciclo singolo e divisione hardware.

Memoria: memoria flash da 32-512 KB integrata su chip. 6-64KB di memoria SRAM.

Orologio, ripristino e gestione dell'alimentazione: alimentazione 2,0-3,6 V e tensione di pilotaggio per l'interfaccia I/O. Ripristino all'accensione (POR), ripristino allo spegnimento (PDR) e rilevatore di tensione programmabile (PVD). Oscillatore a cristallo 4-16 MHz. Circuito oscillatore RC incorporato da 8 MHz regolato prima della fabbrica. Circuito oscillatore RC interno da 40 kHz. PLL per l'orologio della CPU. Cristallo 32kHz con calibrazione per RTC.

Basso consumo energetico: 3 modalità a basso consumo energetico: sospensione, arresto, modalità standby. VBAT per alimentare l'RTC e i registri di backup.

Modalità di debug: debug seriale (SWD) e interfaccia JTAG.

DMA: controller DMA a 12 canali. Periferiche supportate: timer, ADC, DAC, SPI, IIC e UART.

Tre convertitori A/D a 12 bit us-level (16 canali): Intervallo di misurazione A/D: 0-3,6 V. Doppia capacità di campionamento e attesa. Un sensore di temperatura è integrato nel chip.

Convertitore D/A a 12 bit a 2 canali: STM32F103xC, STM32F103xD, STM32F103xE esclusivo.

Fino a 112 porte I/O veloci: a seconda del modello, sono disponibili 26, 37, 51, 80 e 112 porte I/O, tutte mappabili su 16 vettori di interrupt esterni. Tutti tranne gli ingressi analogici possono accettare ingressi fino a 5V.

Fino a 11 timer: 4 timer a 16 bit, ciascuno con 4 IC/OC/PWM o contatori di impulsi. Due timer di controllo avanzato a 16 bit e 6 canali: è possibile utilizzare fino a 6 canali per l'uscita PWM. 2 timer watchdog (watchdog indipendente e watchdog finestra). Timer Systick: contatore decrescente a 24 bit. Per pilotare il DAC vengono utilizzati due timer di base a 16 bit.

Fino a 13 interfacce di comunicazione: 2 interfacce IIC (SMBus/PMBus). 5 interfacce USART (interfaccia ISO7816, LIN, compatibile IrDA, controllo debug). 3 interfacce SPI (18 Mbit/s), di cui due multiplexate con IIS. Interfaccia CAN (2.0B). Interfaccia USB 2.0 a piena velocità. Interfaccia SDIO.

Pacchetto ECOPACK: i microcontrollori della serie STM32F103xx adottano il pacchetto ECOPACK.

effetto di sistema

1. Core ARM Cortex-M3 integrato con memoria Flash e SRAM incorporata. Rispetto ai dispositivi a 8/16 bit, il processore RISC ARM Cortex-M3 a 32 bit offre una maggiore efficienza del codice. I microcontrollori STM32F103xx hanno un core ARM integrato, quindi sono compatibili con tutti gli strumenti e il software ARM.

2. Memoria flash incorporata e memoria RAM: Flash incorporato fino a 512 KB, che può essere utilizzato per memorizzare programmi e dati. È possibile leggere e scrivere fino a 64 KB di SRAM integrata alla velocità di clock della CPU (senza stati di attesa).

3. Memoria statica variabile (FSMC): FSMC è integrato in STM32F103xC, STM32F103xD, STM32F103xE, con 4 selezioni di chip e supporta quattro modalità: Flash, RAM, PSRAM, NOR e NAND. 3 linee di interruzione FSMC sono collegate a NVIC dopo OR. Non esiste FIFO di lettura/scrittura, ad eccezione di PCCARD, i codici vengono eseguiti dalla memoria esterna, l'avvio non è supportato e la frequenza di destinazione è uguale a SYSCLK/2, quindi quando l'orologio di sistema è 72 MHz, l'accesso esterno viene eseguito a 36 MHz.

4. Nested Vectored Interrupt Controller (NVIC): può gestire 43 canali di interrupt mascherabili (escluse 16 linee di interrupt di Cortex-M3), fornendo 16 priorità di interrupt. NVIC strettamente accoppiato raggiunge una latenza di elaborazione degli interrupt inferiore, trasferisce direttamente l'indirizzo della tabella del vettore di immissione degli interrupt al kernel, interfaccia kernel NVIC strettamente accoppiata, consente l'elaborazione anticipata degli interrupt, gestisce gli interrupt con priorità più alta che arrivano in seguito e supporta la catena di coda, salva automaticamente lo stato del processore e la voce di interrupt viene ripristinata automaticamente quando l'interrupt esce, senza l'intervento dell'istruzione.

5. Controller esterno di interrupt/eventi (EXTI): il controller esterno di interrupt/eventi è costituito da 19 linee di rilevamento dei fronti per la generazione di richieste di interrupt/eventi. Ciascuna riga può essere configurata individualmente per selezionare l'evento di trigger (fronte di salita, fronte di discesa o entrambi) e può essere mascherata individualmente. C'è un registro in sospeso per mantenere lo stato delle richieste di interrupt. EXTI è in grado di rilevare quando un impulso sulla linea esterna è più lungo del periodo del clock interno APB2. Fino a 112 GPIO sono collegati a 16 linee di interrupt esterne.

6. Orologio e avvio: è ancora necessario selezionare l'orologio di sistema all'avvio, ma l'oscillatore a cristallo interno da 8 MHz viene selezionato come orologio della CPU durante il ripristino. È possibile selezionare un clock esterno da 4-16 MHz e verrà monitorato per verificarne il successo. Durante questo periodo, il controller è disabilitato e la gestione degli interrupt software viene successivamente disabilitata. Allo stesso tempo, la gestione degli interrupt del clock PLL è completamente disponibile se richiesto (ad esempio in caso di guasto di un oscillatore al quarzo utilizzato indirettamente). È possibile utilizzare più pre-comparatori per configurare la frequenza AHB, inclusi APB ad alta velocità (PB2) e APB a bassa velocità (APB1). La frequenza più alta dell'APB ad alta velocità è 72 MHz e la frequenza più alta dell'APB a bassa velocità è 36 MHz.

7. Modalità di avvio: all'avvio, il pin di avvio viene utilizzato per selezionare una delle tre opzioni di avvio: importazione da Flash utente, importazione da memoria di sistema e importazione da SRAM. Il programma di importazione Boot si trova nella memoria di sistema e viene utilizzato per riprogrammare la memoria Flash tramite USART1.

8. Schema di alimentazione: VDD, l'intervallo di tensione è 2,0 V-3,6 V, l'alimentazione esterna viene fornita tramite il pin VDD, utilizzato per I/O e regolatore di tensione interno. VSSA e VDDA, l'intervallo di tensione è 2,0-3,6 V, ingresso di tensione analogico esterno per ADC, modulo di ripristino, RC e PLL, all'interno dell'intervallo di VDD (ADC è limitato a 2,4 V), VSSA e VDDA devono essere collegati a VSS di conseguenza e VDD. VBAT, l'intervallo di tensione è 1,8-3,6 V, quando VDD non è valido, fornisce alimentazione per RTC, oscillatore a cristallo esterno a 32 KHz e registri di backup (realizzati dalla commutazione dell'alimentazione).

9. Gestione dell'alimentazione: il dispositivo è dotato di un circuito POR (power-on reset) e power-down reset (PDR) completo. Questo circuito è sempre efficace per garantire che vengano eseguite alcune operazioni necessarie quando si parte da 2V o si scende a 2V. Quando VDD è al di sotto di un limite inferiore specifico VPOR/PDR, il dispositivo può anche rimanere in modalità di ripristino senza un circuito di ripristino esterno. Il dispositivo è dotato di un rilevatore di tensione programmabile integrato (PVD). Il PVD viene utilizzato per rilevare VDD e confrontarlo con il limite VPVD. Viene generato un interrupt quando VDD è inferiore a VPVD o VDD è maggiore di VPVD. La routine di servizio di interruzione può generare un messaggio di avviso o mettere l'MCU in uno stato sicuro. PVD è abilitato dal software.

10. Regolazione della tensione: il regolatore di tensione ha 3 modalità operative: principale (MR), basso consumo energetico (LPR) e spegnimento. MR viene utilizzato nella modalità di regolazione (modalità di funzionamento) nel senso tradizionale, LPR viene utilizzato in modalità di arresto e lo spegnimento viene utilizzato in modalità standby: l'uscita del regolatore di tensione è ad alta impedenza, il circuito centrale è spento, incluso consumo zero (il contenuto dei registri e della SRAM non andrà perso).

11. Modalità a basso consumo energetico: STM32F103xx supporta 3 modalità a basso consumo energetico, in modo da ottenere il miglior equilibrio tra basso consumo energetico, tempi di avvio brevi e fonti di riattivazione disponibili. Modalità sospensione: solo la CPU smette di funzionare, tutte le periferiche continuano a funzionare, riattiva la CPU quando si verifica un'interruzione/evento; modalità stop: consente di mantenere il contenuto di SRAM e registri con un consumo energetico minimo. I clock nella regione di 1,8 V sono tutti fermi, gli oscillatori PLL, HSI e HSE RC sono disabilitati e il regolatore di tensione è posto in modalità normale o bassa potenza. Il dispositivo può essere riattivato dalla modalità di arresto tramite una linea di interruzione esterna. La sorgente di interruzione esterna può essere una delle 16 linee di interruzione esterne, un'uscita PVD o un avviso TRC. Modalità standby: alla ricerca del minor consumo energetico, il regolatore di tensione interno è spento, in modo che l'area da 1,8 V sia spenta. Anche gli oscillatori PLL, HSI e HSE RC sono disabilitati. Dopo essere entrati in modalità standby, oltre ai registri di backup e ai circuiti di standby, vengono persi anche i contenuti della SRAM e dei registri. Il dispositivo esce dalla modalità standby quando si verifica un ripristino esterno (pin NRST), ripristino IWDG, fronte di salita sul pin WKUP o avviso TRC. Quando si accede alla modalità di arresto o alla modalità standby, TRC, IWDG e le relative sorgenti di clock non verranno arrestate.